题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

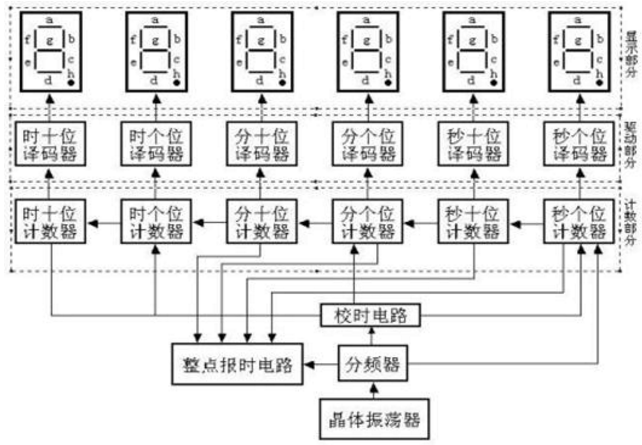

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码

试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石英晶体振荡器(频率为32768Hz)加分频器来实现。译码显示电路将“时”、“分”、“秒”计数器的输出状态经七段显示译码器译码,通过6位LED七段显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是用来对“时”、“分”、“秒”显示数字进行校对调整的。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石…”相关的问题

更多“试设计一个数字电子钟,其原理框图如图9-10所示。秒信号用石…”相关的问题

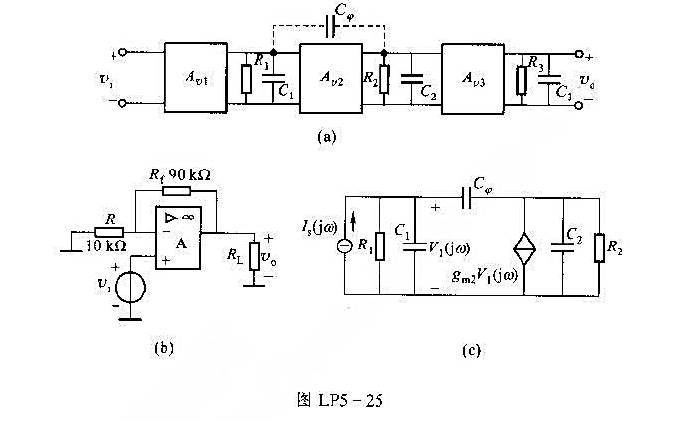

试求两种补偿时所需的电容值.设密勒补偿时

试求两种补偿时所需的电容值.设密勒补偿时 各级的输入和输出电阻对电路影响忽略不计.

各级的输入和输出电阻对电路影响忽略不计.