更多“分析图P5.12所示的电路,列出其状态转换表,说明其逻辑功能…”相关的问题

更多“分析图P5.12所示的电路,列出其状态转换表,说明其逻辑功能…”相关的问题

第4题

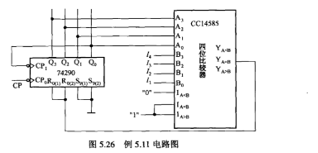

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP≇

图5.26所示为一可变进制计数器,其模数受I4I3I2I1控制.其中,74290已通过将CP1与Q0短接而连成8421BCD码十进制加法计数器的形式,CP0为外部计数输入端, 为异步置0端,

为异步置0端, 为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端,

为异步置9端:CC14585为四位数码比较器,A3A2A1A0、B3B2B1B0为两个比较器的并行数据输入端, 为扩展输入端,

为扩展输入端, 为比较输出端.

为比较输出端.

(1)分析I4I3I2I1=0110时,该电路为多少进制计数器,并画出其状态转换图.

(2)简述该可变进制计数器的工作原理.

第5题

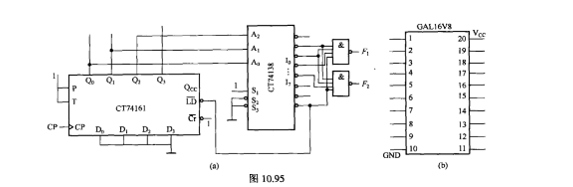

分析图10.95(a)所示电路.(1)画出CT74161(4位二进制加法计数器)Q3Q2Q1Q0的状态

分析图10.95(a)所示电路.(1)画出CT74161(4位二进制加法计数器)Q3Q2Q1Q0的状态

点击查看答案

转换图.假设Q3Q2Q1Q0的初始状态均为0,说明CT74161构成几进制计数器.

(2)说明C174138电路实现的功能.

(3)写出图10.95(a)完成的电路功能符合ABEL语言(GAL16V8如图10.95(b)所示)或VHDL语言的用户原文件(可省略测试向量段).

第6题

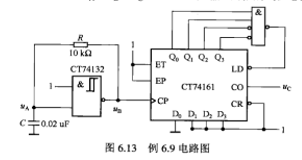

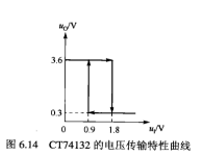

已知TTL集成施密特触发器CT74132和同步4位二进制加法计数器CT74161组成如图6.13所示电路;图6.1

4为CT74132的电压传输特性曲线(CT74161的功能表在此从略,可查阅).

点击查看答案

(1)分别指出图6.13中两部分电路组成什么功能的电路(名称).

(2)分析CT74161组成的电路,画出状态转换图.

(3)试画出uA、uB、uC(CO为进位输出端)的对应波形.

第9题

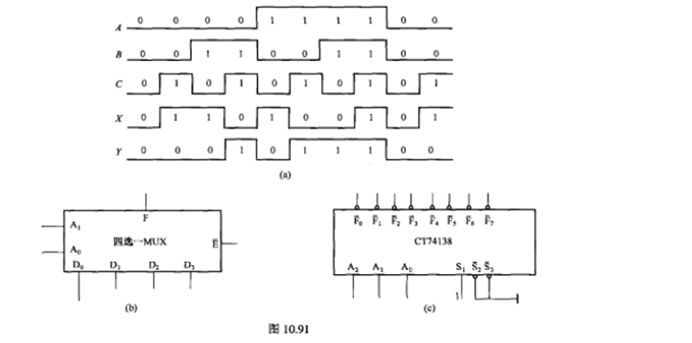

电路的输入A、B、C和输出X、Y的波形如图10.91(a)所示,列出真值表,写出表达式,化简为最简式,分析其

电路的输入A、B、C和输出X、Y的波形如图10.91(a)所示,列出真值表,写出表达式,化简为最简式,分析其

点击查看答案

逻辑功能,并分别用基本逻辑门电路、四选一MUX数据选择器(如图10.91(b))和3-8译码器(如图10.91(c))实现此逻辑电路.

如果结果不匹配,请

如果结果不匹配,请