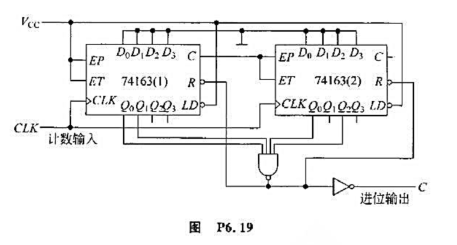

更多“图P6.19是用两个同步十六进制计数器74163接成的计数电…”相关的问题

更多“图P6.19是用两个同步十六进制计数器74163接成的计数电…”相关的问题

第2题

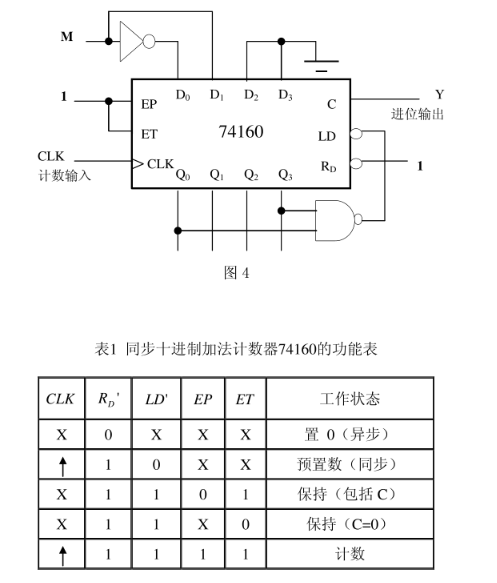

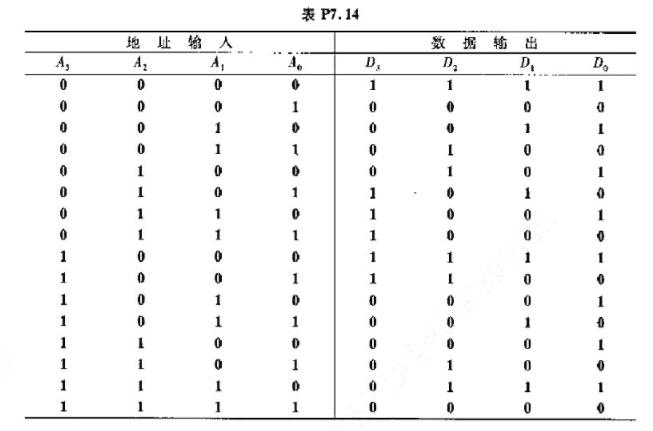

图P7.14是用16x4位ROM和问步十六进制加法计数器74LS161组成的脉冲分频电路,ROM的数据表如表P7

.14所示.试画出在CLK信号连续作用下D3、D2、D1、和D0输出的电压波形,并说明它们与CLK信号频率之比.

点击查看答案

第3题

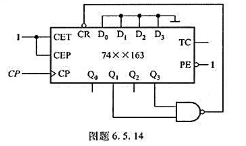

试分析图题6.5.14所示计数器,画出它的状态图,并确定它的模。(74xx163是具有同步清零功能的4位

试分析图题6.5.14所示计数器,画出它的状态图,并确定它的模。(74xx163是具有同步清零功能的4位同步二进制递增计数器,其他功能与74xx161相同)

第4题

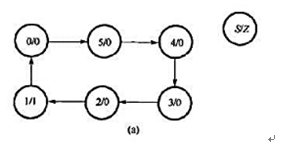

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

第6题

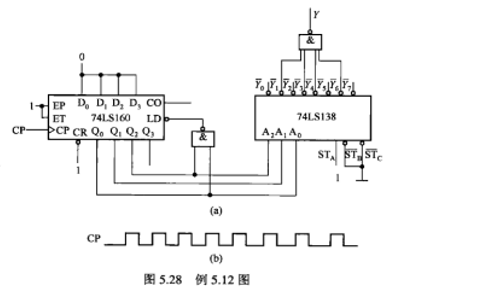

图5.28(a)所示电路为同步十进制加法计数器74160和3-8译码器74138组成的电路,74138输出低电平

图5.28(a)所示电路为同步十进制加法计数器74160和3-8译码器74138组成的电路,74138输出低电平

点击查看答案

有效,使能端处于有效状态.

(1)74160构成多少进制计数器.

(2)假定74160初始状态Q3Q2Q1Q0=0000,试对应图5.28(b)的CP脉冲图画出Q3、Q2、Q1、Q0和Y的输出波形.

第7题

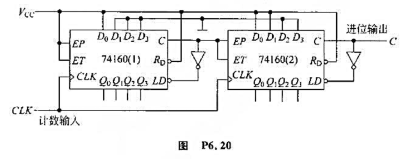

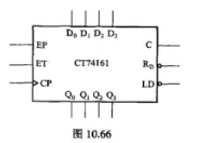

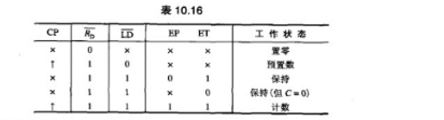

图10.66所示为四位二进制加法计数器,其功能表见表10.16所示.试将两片CT74161采用同步级联方式

及总体反馈归零法设计成一个23进制计数器,要求写出设计过程并画出连接图.

点击查看答案

第8题

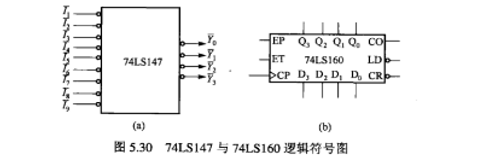

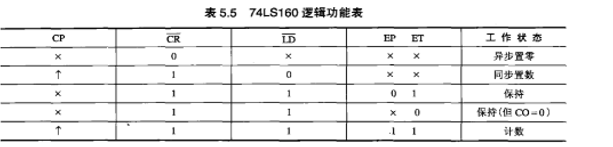

用二-十进制优先编码器74LS147和同步十进制计数器74LS160及其他必要的器件组成可控分频器,当

输入控制信号A、B、C、D、E、F、G、H分别为低电时,输出脉冲与时钟脉冲的分频比分别为1/9、1/8、1/7、1/6、1/5、14、1/3、1/2.请画出电路图.74LS147逻辑符号如图5.30(a)所示,74LS160逻辑符号如图5.30(b)所示,74LS160功能如表5.5所示,Q3、Q2、Q1、Q0为输出端,Q3、Q2、Q1、Q0为置数数据输入端:CO为进位输出,在计数至1001时输出一个时钟周期的高电平.

点击查看答案

第9题

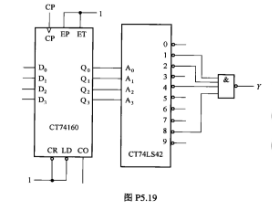

在图P5.19中,CT74160为同步十进制加法计数器,CT74LS42为4-10译码器,设计数器的初始状态为000,

试画出与CP脉冲相对应的Q0,Q1,Q2,Q3及输出Y的波形图.

点击查看答案

如果结果不匹配,请

如果结果不匹配,请