题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

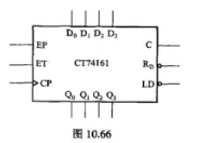

如果要求用计数器CT74161和4-16译码器设计一个12路输出的脉冲分配器,即从电路的12个输出端顺序、循环地输出与时钟正脉冲等宽的负脉冲,则电路应如何连接?试设计电路,井画出电路图.

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“如果要求用计数器CT74161和4-16译码器设计一个12路…”相关的问题

更多“如果要求用计数器CT74161和4-16译码器设计一个12路…”相关的问题

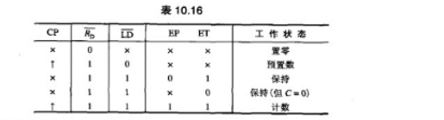

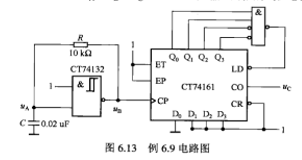

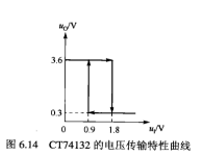

(1)分别指出图6.13中两部分电路组成什么功能的电路(名称).

(2)分析CT74161组成的电路,画出状态转换图.

(3)试画出uA、uB、uC(CO为进位输出端)的对应波形.

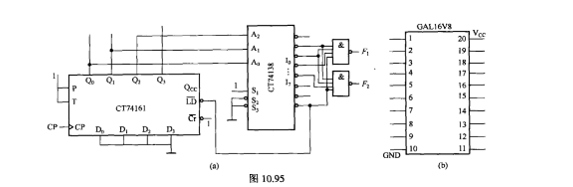

转换图.假设Q3Q2Q1Q0的初始状态均为0,说明CT74161构成几进制计数器.

(2)说明C174138电路实现的功能.

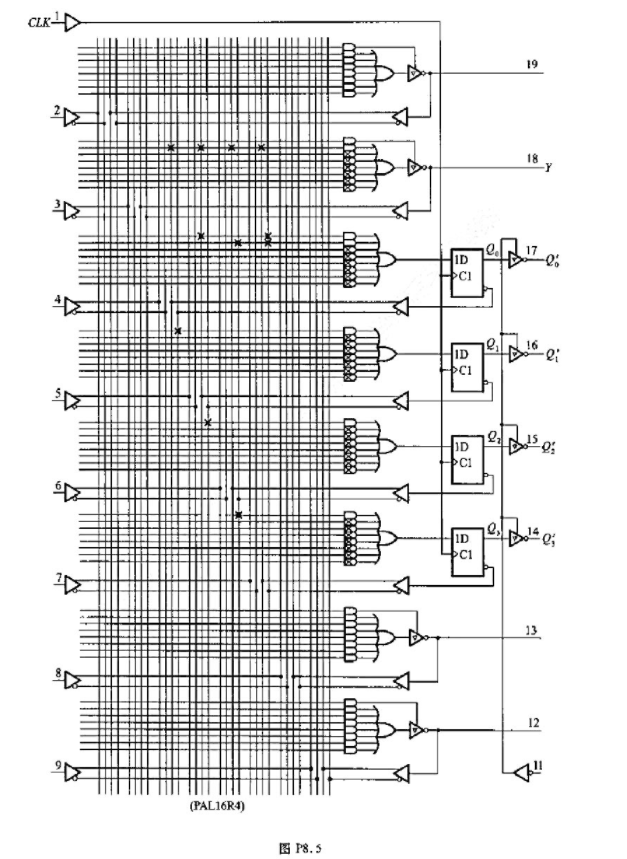

(3)写出图10.95(a)完成的电路功能符合ABEL语言(GAL16V8如图10.95(b)所示)或VHDL语言的用户原文件(可省略测试向量段).

A.00-01-02-03-04-05

B.00-10-20-01-11-12

C.00-01-02-10-11-12

D.00-01-10-11-20-21

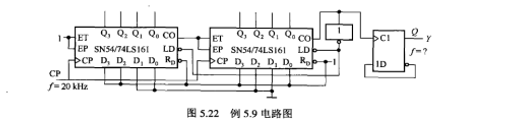

由两片SN54/74LS161(同步4位二进制计数器)组成的同步计数器如图5.22所示.

1)试分析其分频比(即Y与CP之频比),当CP的频率为20kHz时,Y的频率为多少?

2)试用2片SN54/74LS161组成模为91的计数器,要求两片间用级联法,并工作可靠.