题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

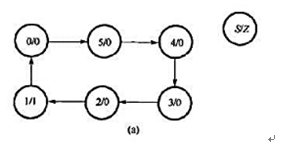

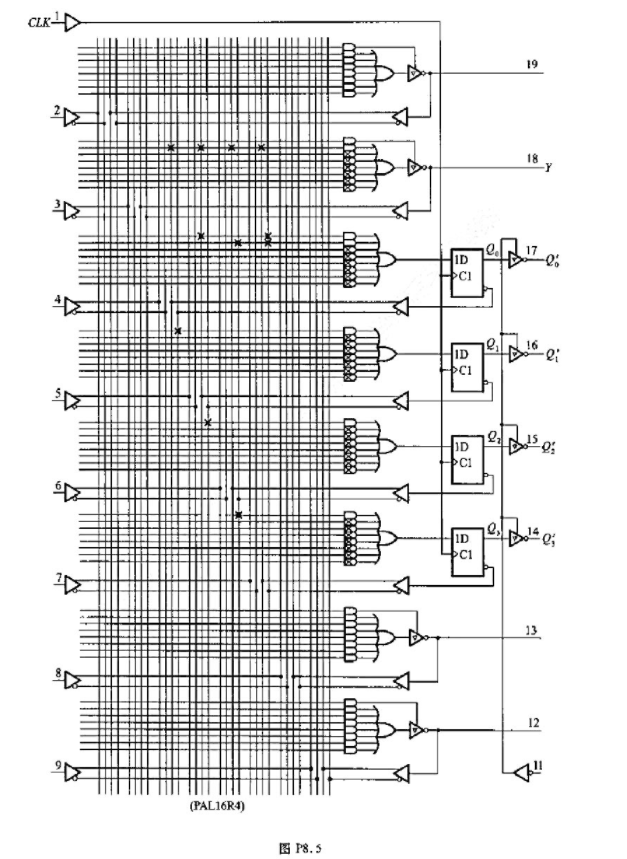

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

采用D触发器设计一个同步计数器,其计数状态转移图如图3.25(a)所示,画出逻辑电路图.

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“采用D触发器设计一个同步计数器,其计数状态转移图如图3.25…”相关的问题

更多“采用D触发器设计一个同步计数器,其计数状态转移图如图3.25…”相关的问题

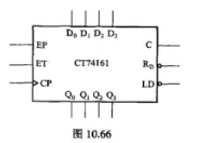

A.同步计数器

B.异步计数器

C.可逆数器

D.步计数器

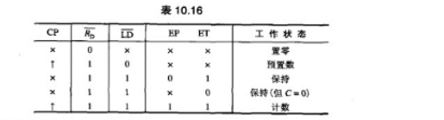

A、十进制计数器

B、单稳态触发器

C、施密特触发器

D、石英晶体多谐振荡器