更多“由或非门构成的基本SR锁存器,当R=S=0时,触发器的状态为…”相关的问题

更多“由或非门构成的基本SR锁存器,当R=S=0时,触发器的状态为…”相关的问题

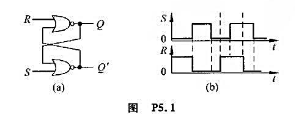

第1题

画出图P5.1(a)中SR锁存器Q和Q'端的电压波形。输入端S和R的电压波形如图P5.1(b)所示。

画出图P5.1(a)中SR锁存器Q和Q'端的电压波形。输入端S和R的电压波形如图P5.1(b)所示。

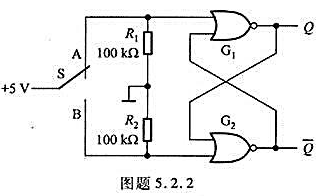

第3题

用CMOS电路74HCT02或非门构成消除机械开关抖动影响的电路如图题5.2.2所示,试画出在开关S由位置

A到B时Q和 端的波形。如改用TTL电路74LS02实现,R1、R2取值的大致范围为多少?整个电路的功耗会发生什么变化?

点击查看答案

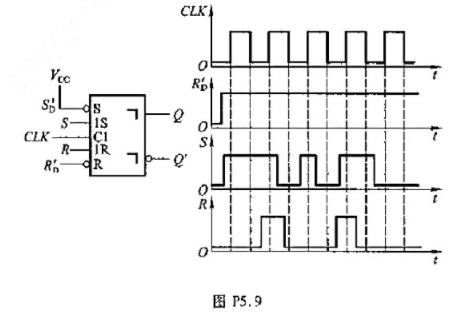

第5题

若主从结构SR触发器的CLK、S、R、R'D</sub>各输入端的电压波形如图P5.9所示,S'D=1试画出Q、Q

若主从结构SR触发器的CLK、S、R、R'D各输入端的电压波形如图P5.9所示,S'D=1试画出Q、Q'端对应的电压波形.

第6题

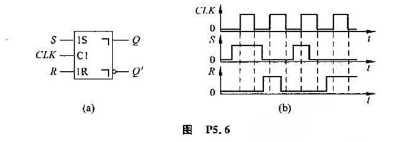

画出图P5.6(a)中脉冲触发SR触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入S、R的电压波形如

画出图P5.6(a)中脉冲触发SR触发器输出端Q和Q'的电压波形。时钟脉冲CLK和输入S、R的电压波形如

点击查看答案

图P5.6(b)所示。设触发器的初始状态为Q=0。

第10题

Verilog程序如下,则下列说法中正确的是()。moduleLearn4_2(A,EN,Y)output[7:0]Y;input[2:0]A;inputEN;reg[7:0]Y;wire[3:0]temp={A,EN};alwayscase(temp)4’b0001:Y=8’b00000001;4’b0011:Y=8’b00000010;4’b0101:Y=8’b00000100;4’b0111:Y=8’b00001000;4’b1001:Y=8’b00010000;4’b1011:Y=8’b00100000;4’b1101:Y=8’b01000000;4’b1111:Y=8’b10000000;default:Y=8’b1111111;endcaseendmodule

A.当EN=1时,将二进制数A转换为其对应的独热码

B.因为缺少break,程序功能将无法实现

C.当EN=0时将输出全部置为1

D.该程序会生成锁存器

如果结果不匹配,请

如果结果不匹配,请