题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

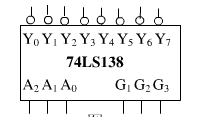

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位进位为Ci。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

用集成3线—8线译码器74LS138和与非门设计一个全加器,设Ai为被加数,Bi为加数,低位进位为Ci-1,和为Si,向高位进位为Ci。

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“用集成3线—8线译码器74LS138和与非门设计一个全加器,…”相关的问题

更多“用集成3线—8线译码器74LS138和与非门设计一个全加器,…”相关的问题

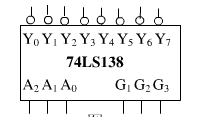

试设计一个三线排队电路,采用3线-8线译码器74138实现。其功能是输入信号A、B、C通过排队电路后,分别由FA、FB、FC输出,且在同一时间只能有一个信号通过。如果同时有两个或两个以上的信号出现,则输入信号按A、B、C的优先顺序通过。

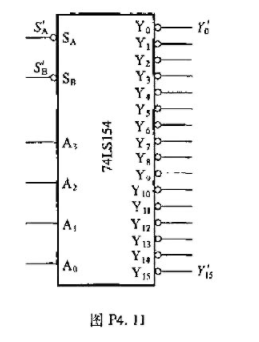

是两个控制端(亦称片选端),译码器工作时应使

是两个控制端(亦称片选端),译码器工作时应使 和

和 同时为低电平.当输人信号A3A2A1A0为0000~111这16种状态时,输出端从

同时为低电平.当输人信号A3A2A1A0为0000~111这16种状态时,输出端从 到Y15依次给出低电平输出信号.

到Y15依次给出低电平输出信号.