题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

[主观题]

设计逻辑电路用4位全加器74LS283完成4位余3码的全加器,可增加门电路或中规模器件实现电路,如编码器74LS148、

数据选择器74LS151、译码器74LS138、4位全加器74LS283,所用器件数不限。

查看答案

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

题目内容

(请给出正确答案)

题目内容

(请给出正确答案)

如果结果不匹配,请 联系老师 获取答案

如果结果不匹配,请 联系老师 获取答案

更多“设计逻辑电路用4位全加器74LS283完成4位余3码的全加器…”相关的问题

更多“设计逻辑电路用4位全加器74LS283完成4位余3码的全加器…”相关的问题

试用4位并行加法器74LS283设计一个加/减运算电路。当控制信号M=0时它将两个输入的4位二进制数相加,而M=1时它将两个输入的4位二进制数相减。两数相加的绝对值不大于15。允许附加必要的门电路。

能否用一片4位并行加法器74LS283将余3代码转换成8421的二-十进制代码?如果有可能,应当如何连线?

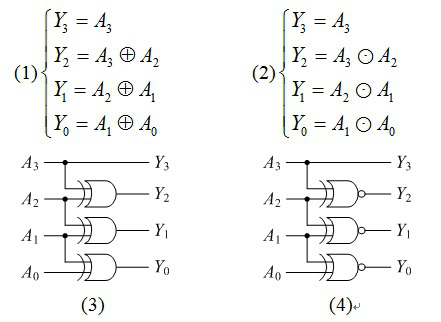

A.(1)和(3)

B.(1)和(4)

C.(2)和(3)

D.(2)和(4)

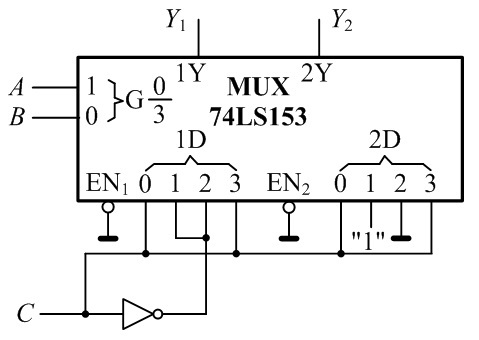

A.该电路实现全加器的逻辑功能,Y1为和的输出,Y2为进位输出

B.该电路实现一致性判别的逻辑功能,Y1是判别为一致时的输出,Y2为不一致的输出

C.该电路实现奇偶校验的逻辑功能,Y1为奇数输出,Y2为偶数输出

D.该电路实现全减器的逻辑功能,Y1为差的输出,Y2为借位输出